محتويات المقال

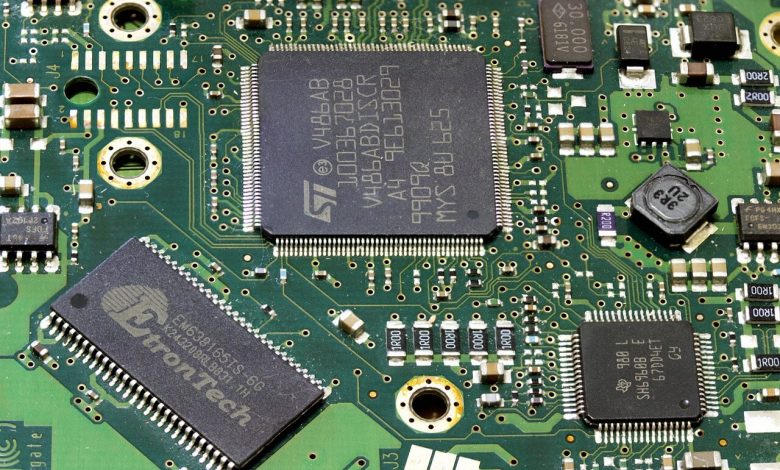

يعد إتقان مخطط دبابيس معالج Intel 8086 أمراً بالغ الأهمية لمهندسي الأجهزة والطلاب الذين يحاولون فهم الأسس المعمارية لأنظمة 16 بت. يعاني العديد من المطورين من صعوبة في تكوين النواقل المتعددة الإرسال وأنظمة التشغيل المزدوجة، مما يؤدي غالباً إلى أخطاء فادحة في اتصالات الأجهزة. ومن خلال فك تشفير الوظائف الدقيقة لهذه الشريحة التاريخية المكونة من 40 دبوساً، يمكن لمصممي الأنظمة دمج البروتوكولات القديمة بنجاح في الأنظمة المدمجة الحديثة.

تم إصدار هذا المعالج بواسطة شركة Intel في عام 1978، وهو يستخدم تقنية أشباه الموصلات المعدنية المؤكسدة عالية الأداء (HMOS) ويعمل بمصدر طاقة قياسي بجهد 5 فولت. يتميز المعالج بناقل عناوين مكون من 20 خطاً قادراً على الوصول إلى مساحة 1 ميجابايت من الذاكرة، مقترناً بناقل بيانات مكون من 16 خطاً. ولتجميع هذه التوصيلات فعلياً داخل شريحة IC المكونة من 40 دبوساً، قامت الشركة المصنعة بذكاء بمضاعفة خطوط العناوين الستة عشر السفلية مع خطوط البيانات، وخطوط العناوين الأربعة العلوية مع إشارات حالة الأجهزة.

تكوينات الدبابيس العامة (من 1 إلى 23، ومن 33 إلى 40)

بغض النظر عن حالة التشغيل، تحتفظ 32 وظيفة محددة للدبابيس بنفس الأداء عبر جميع إعدادات الأجهزة. يتلقى المعالج طاقته من خلال طرف VCC عند الدبوس 40، بينما يعمل الدبوسان 1 و 20 كوصلات أرضية من نوع VSS. وتحتل خطوط ناقل العناوين والبيانات المتعددة الإرسال، والتي تحمل التصنيف من AD0 إلى AD15، الدبابيس من 2 إلى 16، بالإضافة إلى الدبوس 39.

تتم مضاعفة خطوط العناوين العلوية، من A16 إلى A19، مع إشارات الحالة من S3 إلى S6 على الدبابيس من 35 إلى 38. وتوفر إشارات الحالة هذه ملاحظات تشغيلية في الوقت الفعلي؛ فعلى سبيل المثال، يعمل طرف S5 كعلم مقاطعة، بينما يشير طرف S6 إلى التحكم الحالي في الناقل الرئيسي. وتشمل الأطراف الأخرى الثابتة والحاسمة ما يلي:

- الدبوس 34 (BHE/S7): تمكين الناقل العالي، والذي يؤكد وجود البيانات على البايت العلوي من الناقل.

- الدبوس 32 (RD): إشارة منخفضة نشطة تشير إلى عملية قراءة من الذاكرة أو من أجهزة الإدخال والإخراج.

- الدبوس 19 (CLK): يستقبل إشارة الساعة الخارجية لمزامنة جميع عمليات المعالج الدقيق الداخلية.

- الدبابيس 17 و 18 (NMI و INTR): تتعامل مع طلبات المقاطعة غير المقنعة وطلبات المقاطعة القياسية، على التوالي.

- الدبابيس 21 و 22 و 23: تدير عملية إعادة التعيين (RESET)، وإقرارات حالة الاستعداد (READY)، وتعليمات انتظار الاختبار (TEST).

خطوات عملية: كيفية تكوين أوضاع التشغيل

الميزة المحددة لمعالج Intel 8086 هي قدرته على التوسع من الأجهزة الإلكترونية البسيطة إلى بنيات الخوادم المعقدة. يتم التحكم في هذا بالكامل من خلال طرف أجهزة واحد. اتبع هذه الخطوات لتكوين وضع التشغيل بشكل صحيح:

- حدد موقع الدبوس 33، والمصنف كطرف MN/MX على الدائرة المتكاملة.

- لبناء نظام مستقل بمعالج واحد، قم بتطبيق إشارة عالية ( 1 ) على الدبوس 33. هذا ينشط الوضع الأدنى (Minimum Mode).

- لتصميم بيئة معالجات متعددة، قم بتطبيق إشارة منخفضة ( 0 ) على الدبوس 33. هذا يشغل الوضع الأقصى (Maximum Mode).

- بمجرد تعيين الوضع، يجب عليك إعادة تعيين الدبابيس من 24 إلى 32، حيث تتغير وظائفها الكهربائية بالكامل بناءً على اختيارك.

تعريفات الدبابيس الخاصة بالوضع (من 24 إلى 32)

عندما يغير المعالج الدقيق أوضاعه، تتكيف الدبابيس من 24 إلى 32 لدعم التحكم المباشر في الأجهزة الطرفية أو التحكيم بين المعالجات المتعددة. يوضح الجدول التالي صراحة كيف تتغير هذه الأطراف المحددة بناءً على الوضع النشط.

| رقم الدبوس | وظيفة الوضع الأدنى (معالج واحد) | وظيفة الوضع الأقصى (معالجات متعددة) |

|---|---|---|

| الدبوس 24 | إشارة INTA (إقرار المقاطعة) | إشارة QS0 (حالة قائمة الانتظار) |

| الدبوس 25 | إشارة ALE (تمكين مزلاج العنوان) | إشارة QS1 (حالة قائمة الانتظار) |

| الدبوس 26 | إشارة DEN (تمكين البيانات) | إشارة S0 (حالة منخفضة نشطة) |

| الدبوس 27 | إشارة DT/R (إرسال/استقبال البيانات) | إشارة S1 (حالة منخفضة نشطة) |

| الدبوس 28 | إشارة M/IO (اختيار الذاكرة أو الإدخال/الإخراج) | إشارة S2 (حالة منخفضة نشطة) |

| الدبوس 29 | إشارة WR (عملية الكتابة) | إشارة LOCK (قفل الناقل) |

| الدبوس 30 | إشارة HLDA (إقرار الحجز) | إشارة RQ/GT0 (طلب/منح الوصول) |

| الدبوس 31 | إشارة HOLD (طلب حجز الناقل) | إشارة RQ/GT1 (طلب/منح الوصول) |

رؤية تحليلية: العبقرية الاستراتيجية في الإرسال المتعدد

يظل التصميم المعماري لمعالج Intel 8086 درساً احترافياً في التغلب على قيود الأجهزة المادية. في أواخر السبعينيات، كان تصنيع شريحة بأكثر من 40 دبوساً أمراً باهظ التكلفة ومعرضاً للفشل المادي. ومن خلال مضاعفة ناقل العناوين المكون من 20 بت مع ناقل البيانات المكون من 16 بت (من AD0 إلى AD15)، تمكن مهندسو شركة Intel من دمج قدرات حوسبة هائلة في حزمة DIP قياسية وفعالة من حيث التكلفة. هذا الخيار التصميمي الدقيق هو بالضبط ما سمح لثورة الحوسبة الشخصية بأن تظل ميسورة التكلفة.

علاوة على ذلك، كان إدراج طرف MN/MX عند الدبوس 33 بمثابة ضربة من البصيرة الاستراتيجية. فبدلاً من تصميم شريحتين منفصلتين لقطاعات السوق المختلفة، ابتكرت الشركة المصنعة معالجاً موحداً يمكنه الانتقال بسلاسة من الأجهزة الإلكترونية الاستهلاكية الرخيصة (الوضع الأدنى) إلى خوادم المؤسسات المتطورة (الوضع الأقصى). إن فهم مخطط الدبابيس الدقيق هذا ليس مجرد درس في تاريخ التكنولوجيا؛ بل هو دراسة أساسية في الهندسة الإلكترونية القابلة للتوسع والتي تستمر في التأثير على تصميمات الأنظمة على شريحة (SoC) الحديثة اليوم.